-

ソリューション

-

WL-CSP構造と特徴

-

WL-CSP新規技術

-

信頼性データ

WL-CSP

スマートフォン、ウエアラブル機器向けの小型/薄型パッケージ

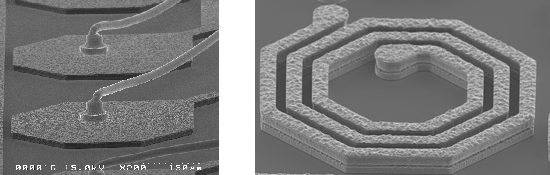

○モールド構造による高信頼性、多くの車載実績

○モールドレス構造による薄型、狭端子ピッチの実現

○お客様のニーズを実現する共同開発体制

○ウエハ加工~個片出荷までの一貫生産体制

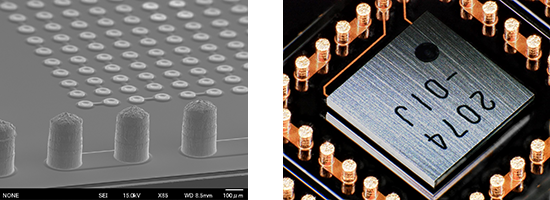

Cu配線

Power、高周波、MEMS製品の特性向上/小型化/多機能化

○厚付けCu配線によるオン抵抗低減

○Alパッド配置フリー化、IOパッド縮小によるチップサイズ縮小化

○層間絶縁膜の厚膜化による高耐圧対応

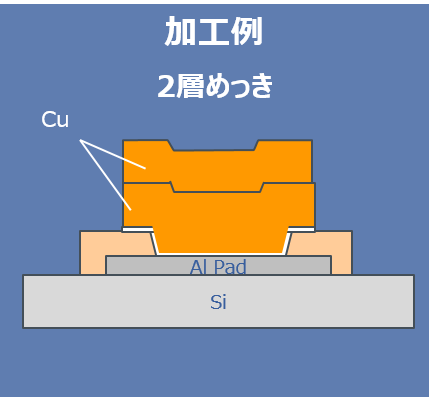

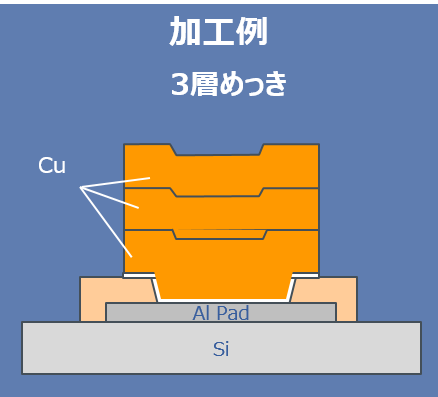

○多層配線による高機能化

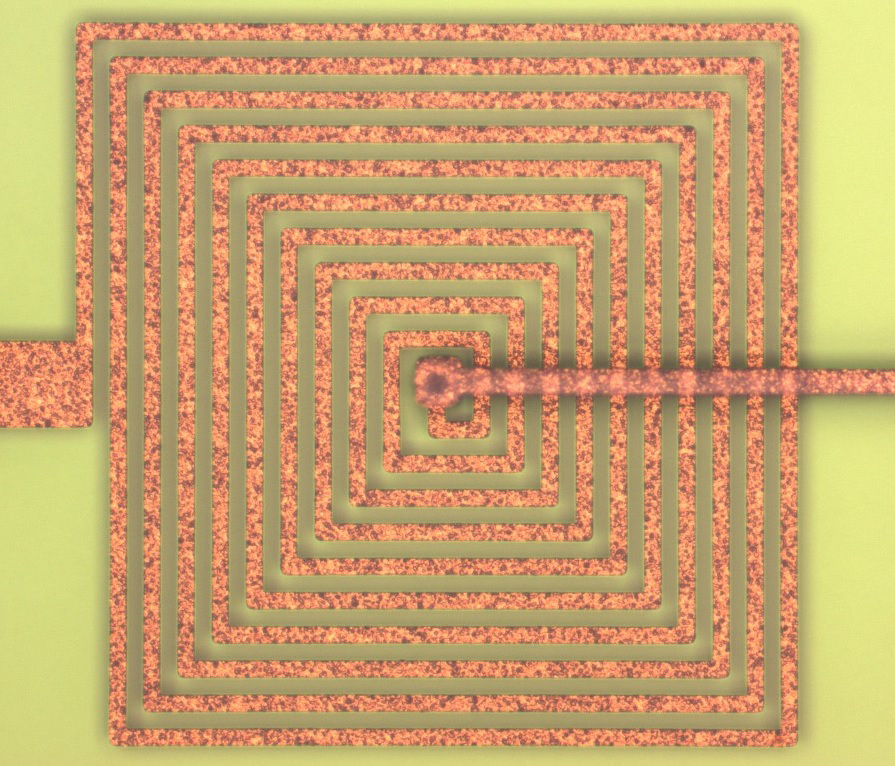

○コイル等素子形成による小型化、高機能化

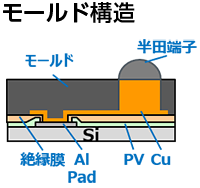

マルチチップ

ラピスセミコンダクタの技術を集結した次世代パッケージ

○Cu配線技術/高Cu Pillar形成技術/実装技術の融合によるマルチチップ化、モジュール化、Fan Out化の実現

○接続用部材(ワイヤ、基板等)の削除による配線抵抗の低減

○モールド構造による高信頼性確保

■ニーズに対応できるラインナップを取り揃えて提案いたします。

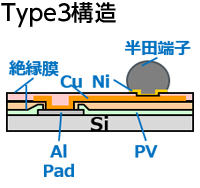

(1)高信頼性、大チップ、応力にセンシティブな製品、2層配線には、モールドTypeを推奨

(2)薄型が求められる製品には、モールドレスTypeを推奨

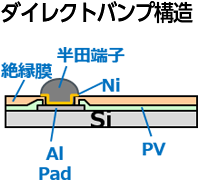

(3)狭ピッチ(0.10~0.3mm)端子が求められる製品には、モールドレスTypeを推奨

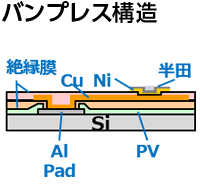

(4)基板内蔵用(端子不要)には バンプレス構造を推奨

(5)デバイスのAl Padが端子位置にレイアウト可能な場合には、ダイレクトバンプ構造を推奨

(6)その他、バックサイドコート・裏面処理・多層配線・低温絶縁膜・端子処理(Sn-Ag/Au/Niメッキ)等のカスタマイズが可能

| モールドType | モールドレスType | |||

| 構造 |  |

|

|

|

| 特徴 | 高信頼性を確保 (AEC-Q100 G0) |

ファインピッチ端子 最薄Type |

基板内蔵用の 端子処理 |

ファインピッチ端子 最薄Type廉価版 |

| 薄型(取り付け高さ) | 0.3mm以上 | 0.2mm以上 | 0.2mm以上 | 0.2mm以上 |

| 端子ピッチ | 0.3mm以上 | 010mm以上 | 010mm以上 | 010mm以上 |

| 端子径 | 150um~ | 75um~ | 75um~ | 75um~ |

| 端子高さ | 60um~250um | 20um~250um | 6um~ | 20um~250um |

ラピスセミコンダクタが提供する端子ピッチのラインナップ

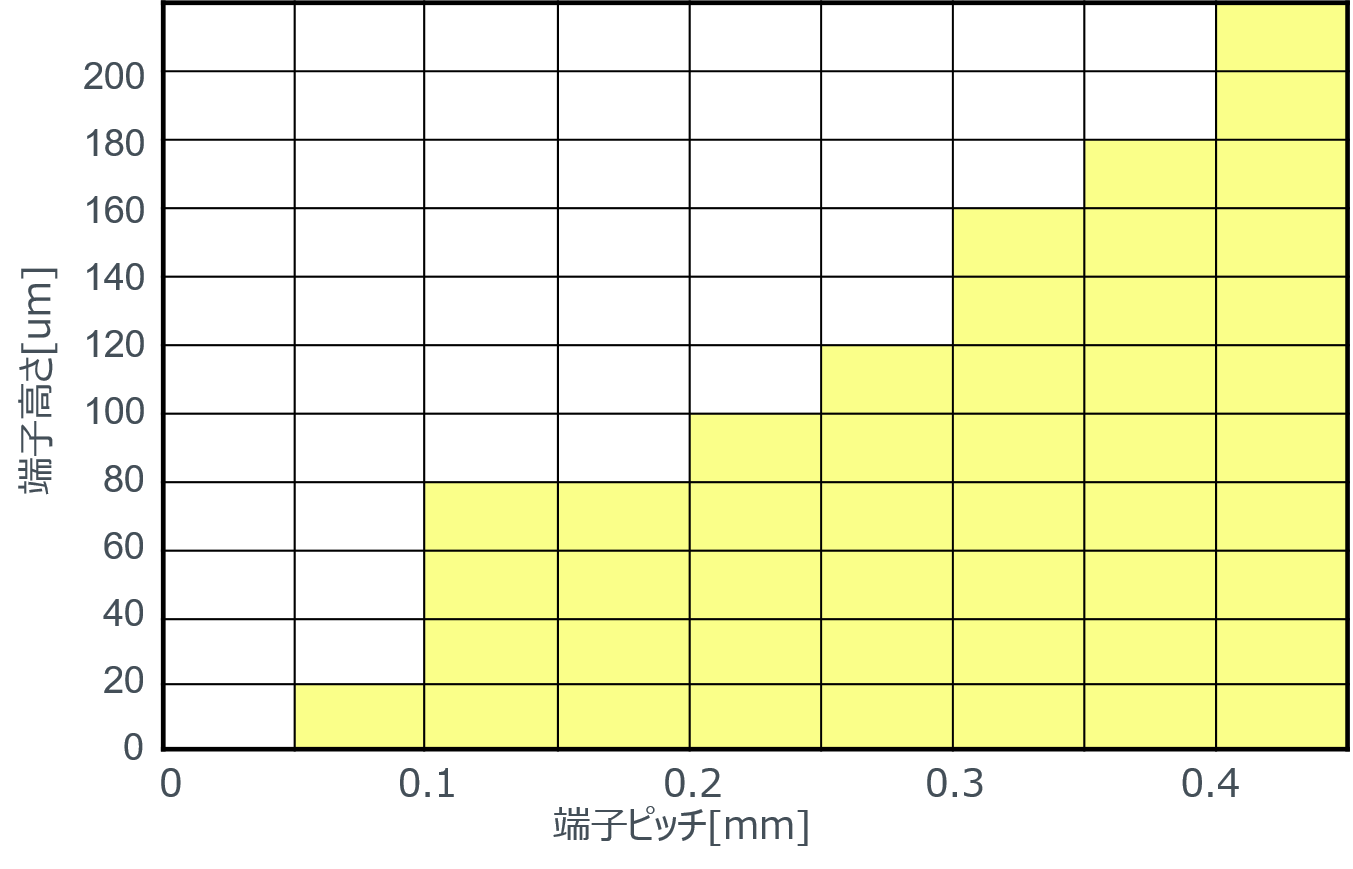

受託フローおよび加工サービス内容

デバイス特性向上を可能にする厚Cu再配線技術

①Cu配線によるオン抵抗の低減、放熱性の向上

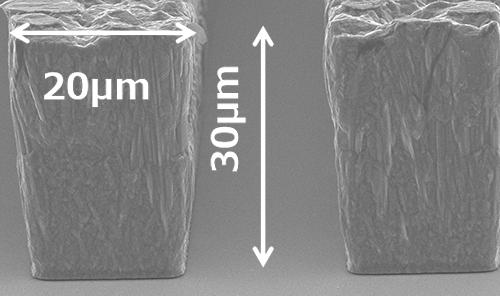

②超厚付け( ~30μm )Cu配線によるワイヤーボンド時タメージ防止

③Cu配線+Cuワイヤ接合による接続信頼性向上

④レジストの積層技術(界面改質等)

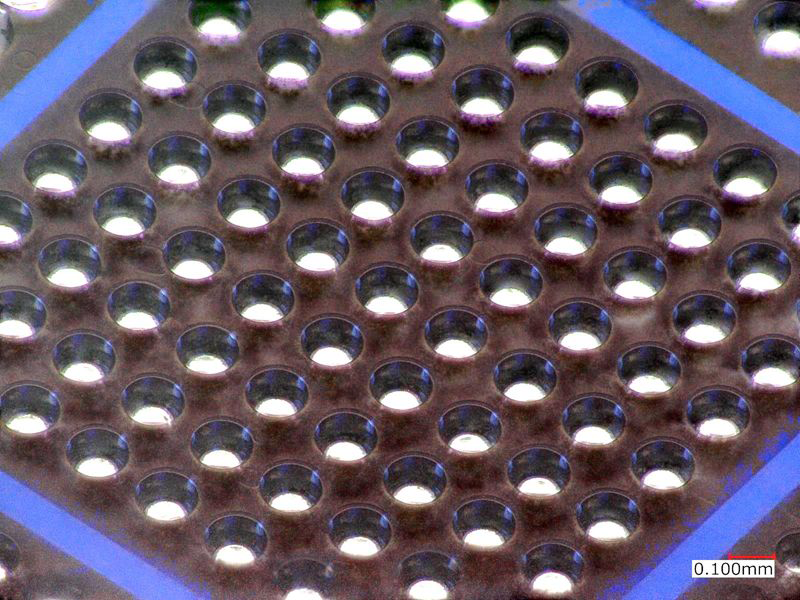

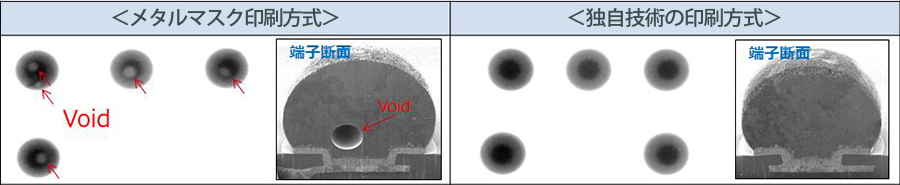

ファインピッチ/高端子/ボイドレスを実現する端子形成技術

〇メタルマスク印刷製法では実現不可能なファインピッチかつ高端子の構造が形成可能です

〇ファインピッチで課題となる端子ボイドに対し、独自の技術によりボイドレス化を実現しています

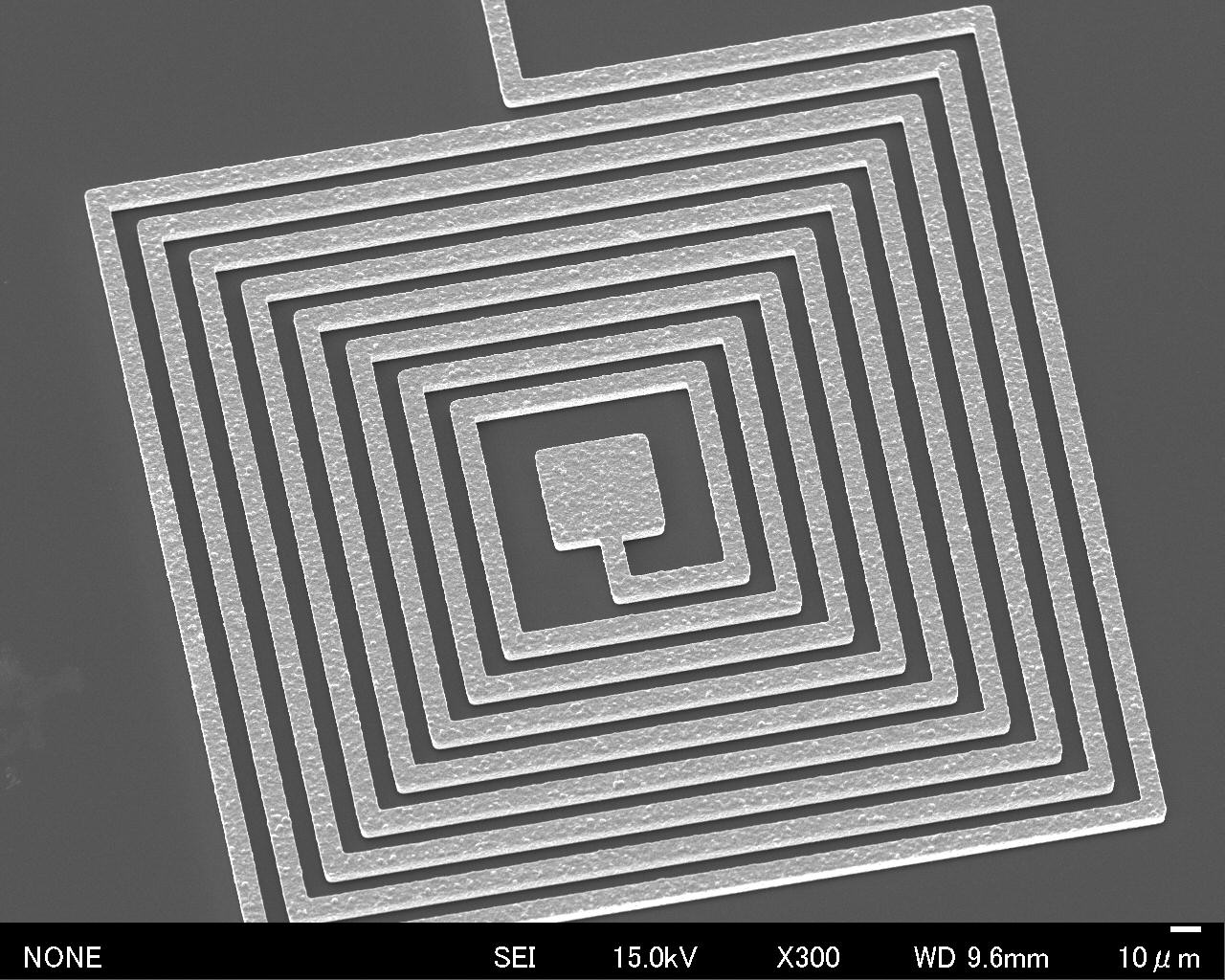

業界最高峰の微細再配線(L/S=8/8μm)/極小Via(Φ8μm)形成技術

〇Cu厚≦5umにて、Line/Space=8/8 μm再配線を対応可能(量産実績あり)

〇Min L/S=6/6 μmまで試作対応可(実績あり)

〇再配線上へMin Φ8 μmのVia形成可

〇絶縁膜はLow k材料対応可(高周波用途での採用実績あり)

AEC-Q100 『グレード0』相当の信頼性データを保有

■モールド Type【グレード0】

| 試験項目 | 試験条件 | 備考 |

| Pre-condition (前処理) | 85℃/85% RH, 168H, reflow 260℃ | Package Level |

| High Temp.Storage(高温放置) | Ta=150℃, 2000H | Package Level |

| Temp. Cycle *1(温度サイクル) | -65℃~RT~175℃, 500cyc | Package Level & Board Level |

■モールドレス Type【グレード1】

| 試験項目 | 試験条件 | 備考 |

| Pre-condition (前処理) | 85℃/85% RH, 168H, reflow 260℃ | Package Level |

| High Temp.Storage(高温放置) | Ta=150℃, 1000H | Package Level |

| Temp. Cycle *1(温度サイクル) | -65℃~RT~150℃, 500cyc | Package Level & Board Level |